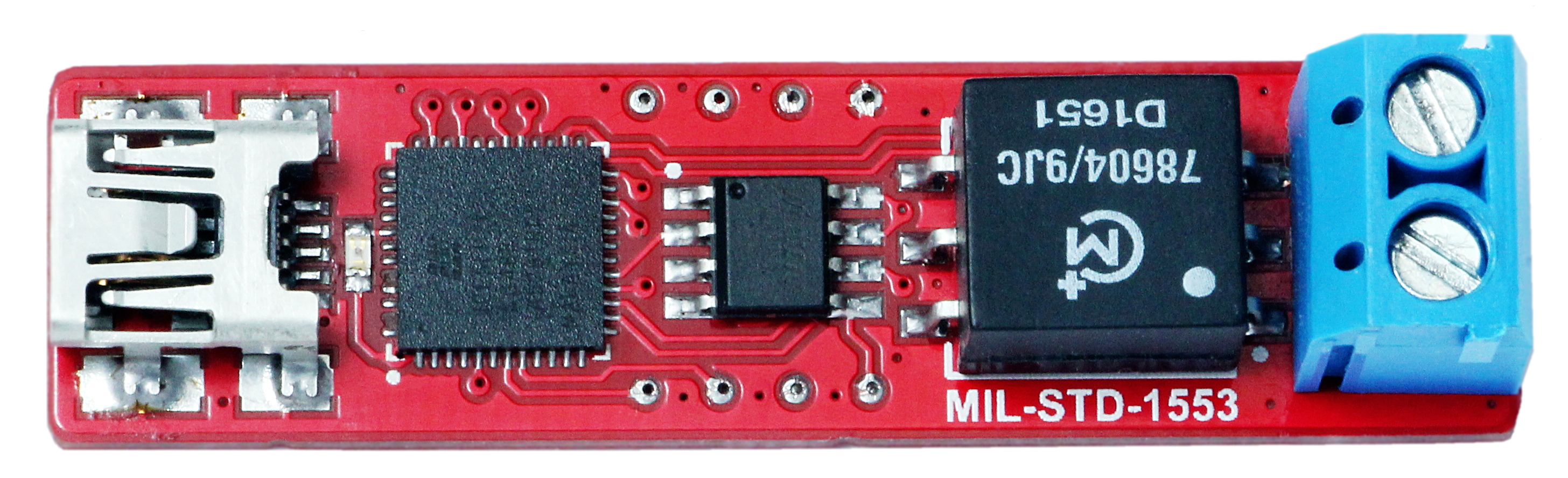

MIL-STD-1553 FPGA Network Traffic Emulator

|

|

|

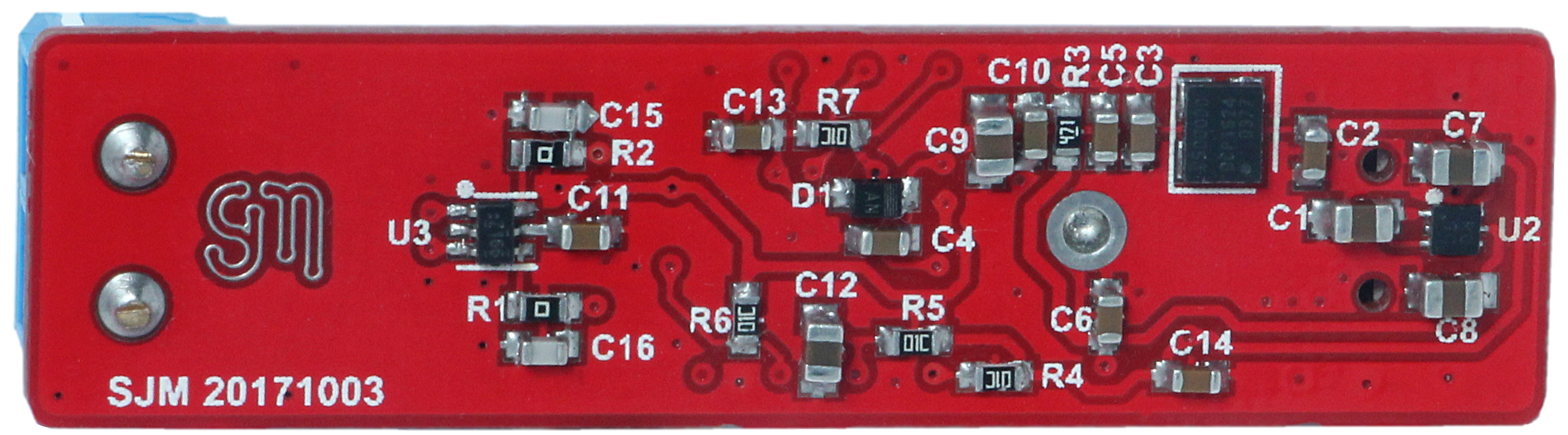

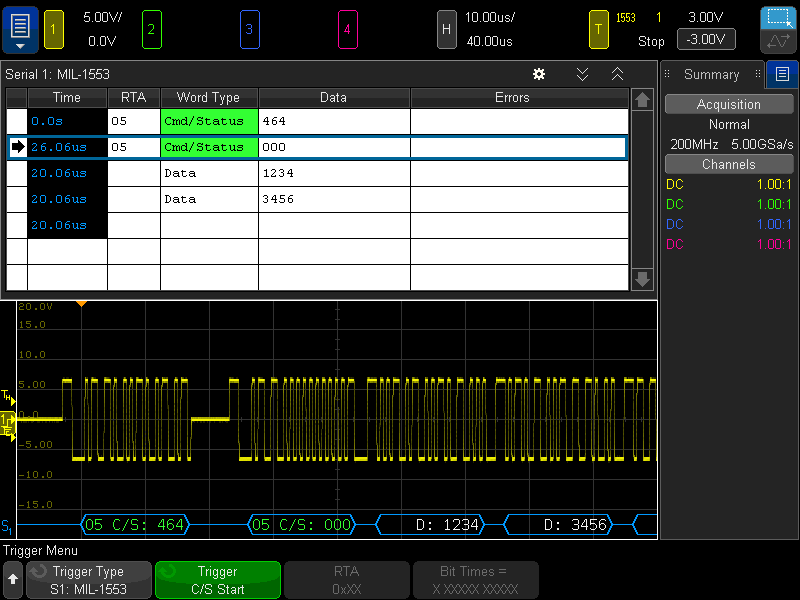

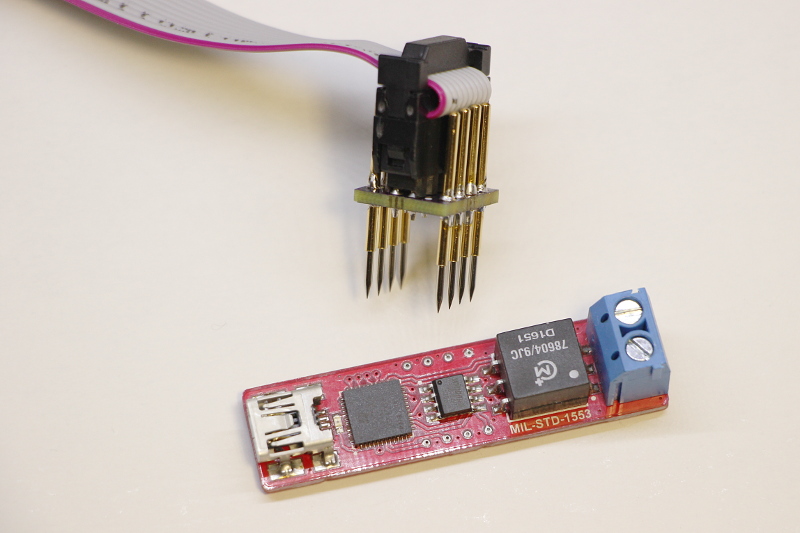

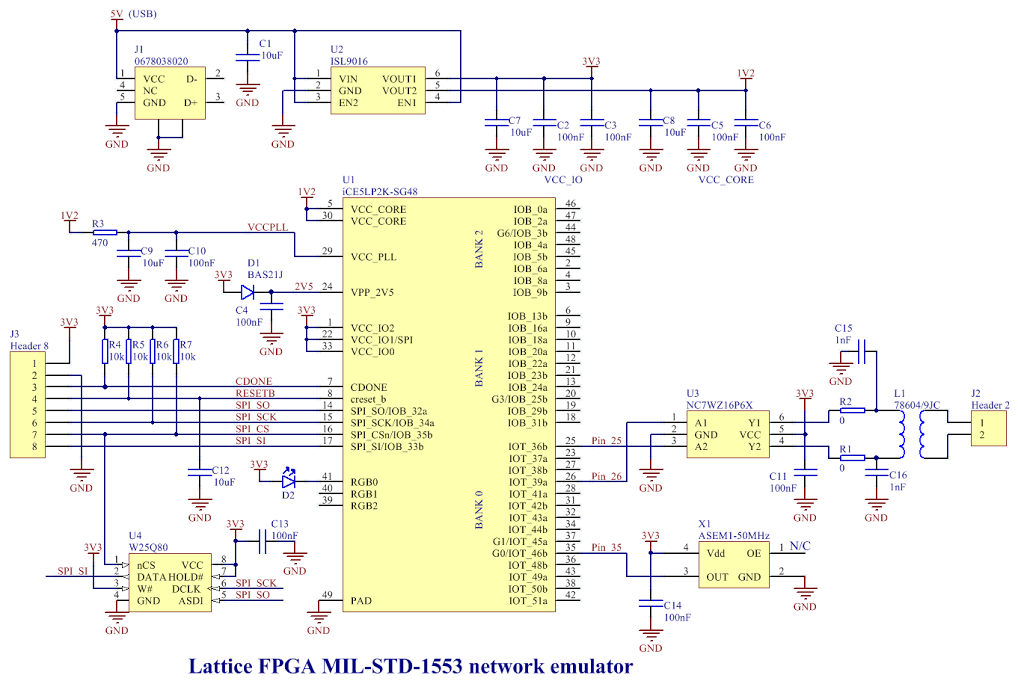

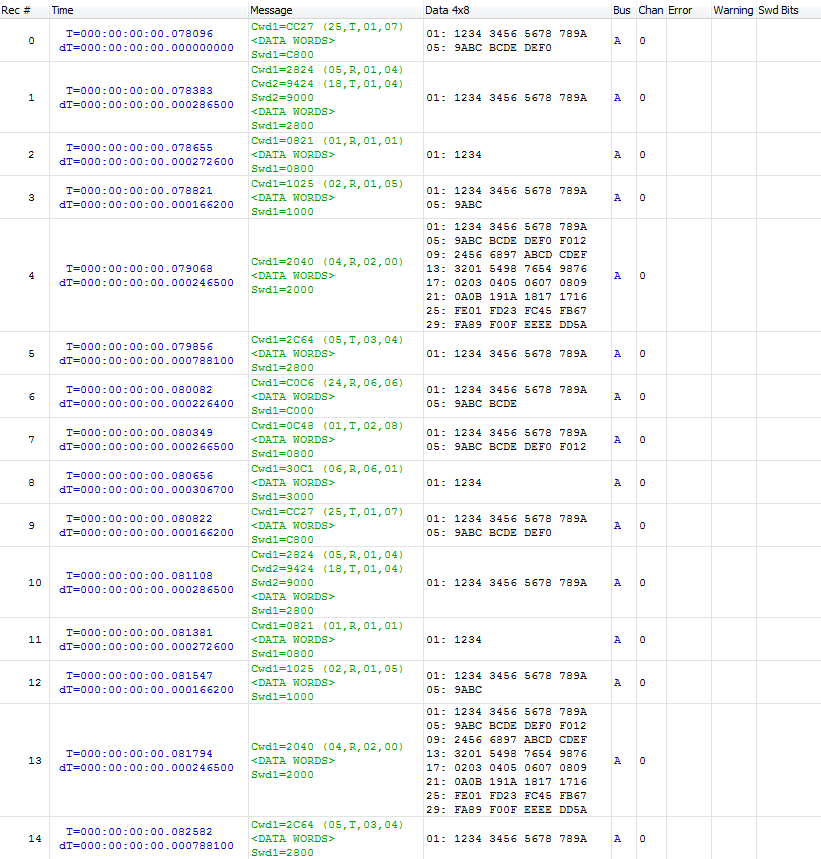

This project uses a Lattice iCE40 Ultra FPGA (iCE5LP2k) to emulate traffic on a MIL-STD-1553 network. It simulates transmissions on the bus and includes messages sent from a BC to a number of different RTs. It also includes the status responses from each of the RTs to the BC. It covers BC-RT, RT-BC and RT-RT transfers. The output is electrically isolated, providing a degree of protection to both the FPGA and other network devices. The PROM is programmed using a bed-of-nails pogo-pin adapter. A breathing LED provides operational status indication.

Right-click to open larger images below. |

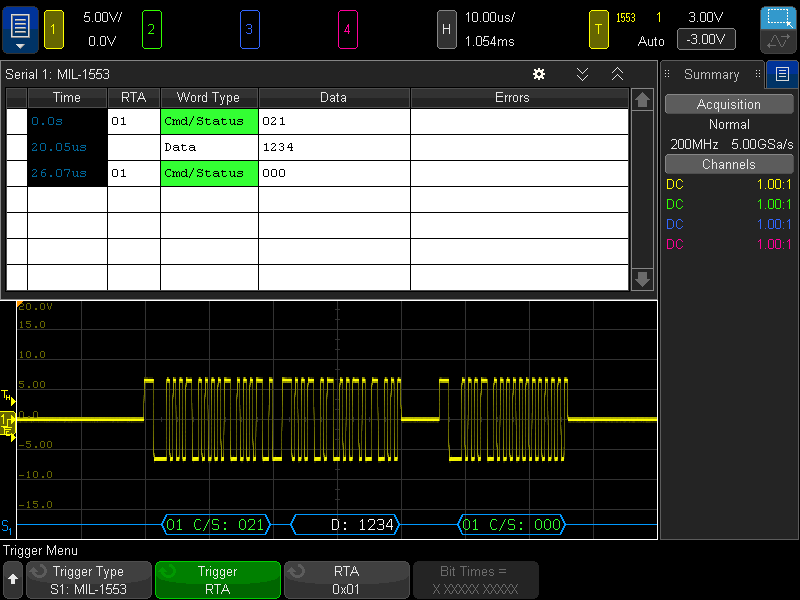

Typical BC-RT |

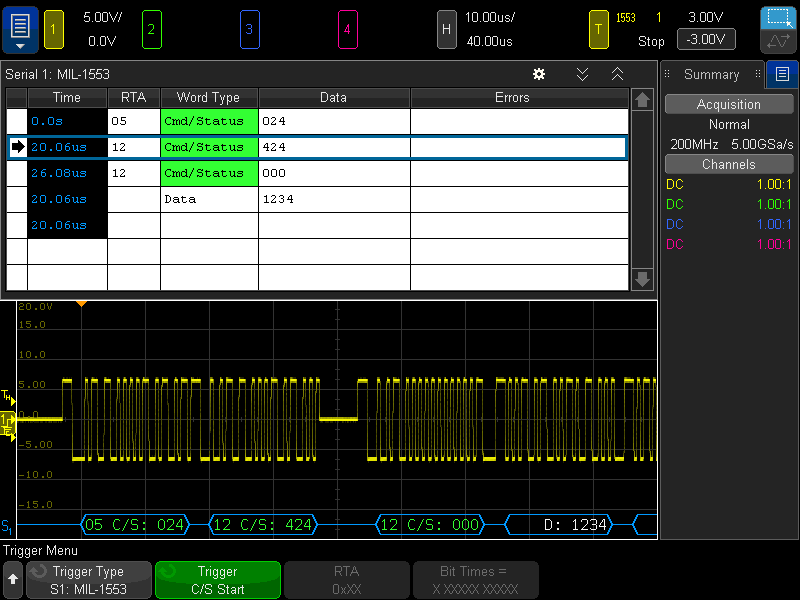

Typical RT-RT |

Typical RT-BC |

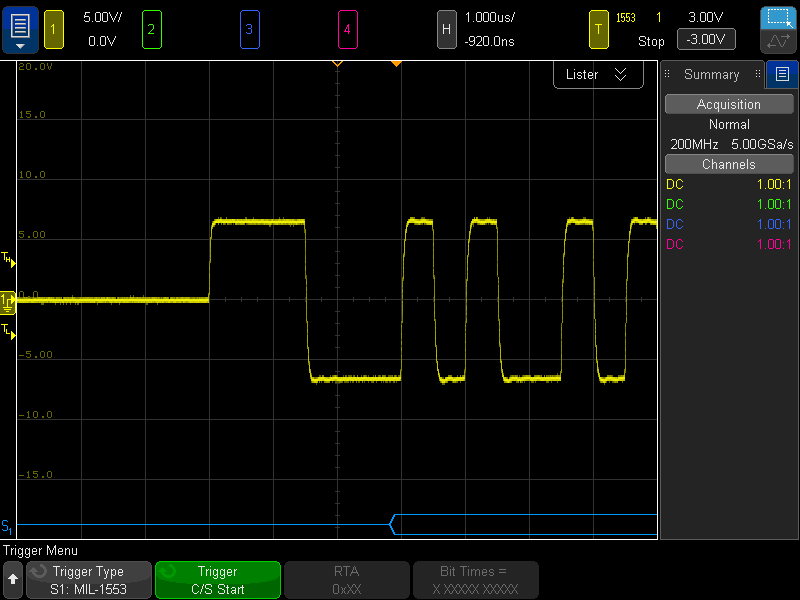

Sync pulse |

Programming adapter |

Schematic |

Typical network simulation showing BC-RT, RT-BC and RT-RT

|

|